PowerPC E500 MMU详解

1. 什么是MMU?

MMU是Memory Management Unit的缩写,中文名称为内存管理单元。MMU是负责处理器(CPU)的内存访问请求的计算机硬件,其功能包括虚拟地址到物理地址的转换(即虚拟内存管理)、内存保护、缓存cache的控制等。

MMU是一个与软件密切相关的硬件部件,也是运行linux等依赖MMU内存管理单元操作系统内核机制的最大部件之一。如果处理器没有MMU,CPU内部执行单元产生的内存地址信号将直接通过地址总线发送到芯片引脚,被内存芯片接收,这就是物理地址(physical address),简称PA。英文physical代表物理的接触,所以PA就是与内存芯片physically connected的总线上的信号。

如果MMU存在且启用,CPU执行单元产生的地址信号在发送到内存芯片之前将被MMU截获,这个地址信号称为虚拟地址(virtual address),简称VA,MMU会负责把VA翻译成另一个地址,然后发到内存芯片地址引脚上,即VA映射成PA。

2. PowerPC E500 MMU

PowerPC(Performance Optimization With Enhanced RISC – Performance Computing,有时简称PPC)是一种精简指令集(RISC)架构的中央处理器(CPU),其基本的设计源自IBM(国际商用机器公司)的POWER(Performance Optimized With Enhanced RISC)。

PowerPC芯片凭借其出色的性能和高度整合和技术先进特性在网络通信应用,工业控制应用,家用数字化,网络存储领域,军工领域,电力系统控制等都具有非常广泛的应用。

PowerPC的E500是飞思卡尔(FreeScale)基于Power Architecture的32位微处理器核心。E500系列核心有三个版本,即E500v1,E500v2的E500mc。64位版本的E500mc演变为E5500核心,并于2010年推出。

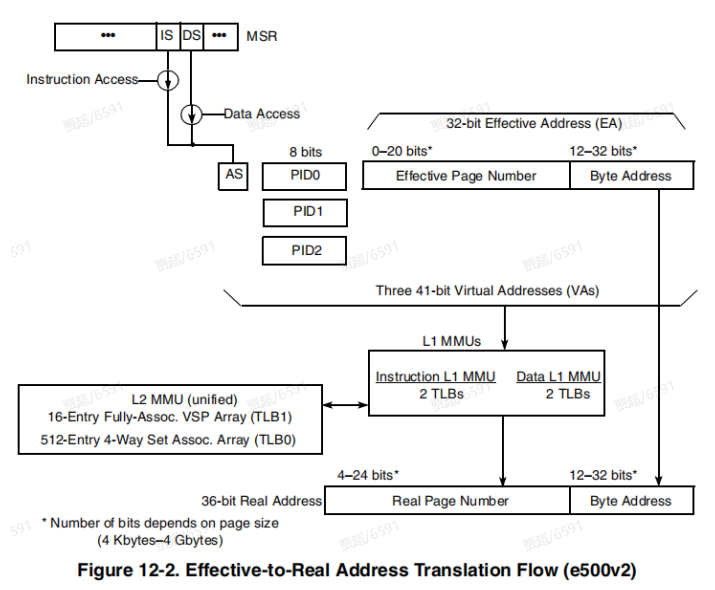

PowerPC E500 核心(后简称“E500”)采用了两级内存管理单元(MMU)体系结构。L1-MMU、L2-MMU为该结构中的两个硬件单元。E500通过L1-MMU和L2-MMU,以及一些辅助寄存器和指令来实现虚实地址的转换。E500v1核心是把32位有效地址转换为32位物理地址(使用41位临时虚拟地址);E500v2核心是把32位有效地址转换为36位物理地址。

L1-MMU特性:

1. 两个4条目的全关联TLB数组(一个用于指令访问,一个用于数据访问支持9种(E500v1)或11种(E500v2)页面大小,即I-L1VSP和D-L1VSP

2. 两个64 entry, 4路set-associative TLB数组(一个用于指令访问,一个用于数据访问),仅支持4kbyte页面,即I-L1TLB4K和D-L1TLB4K。

3. L1 MMU访问与L1缓存访问(地址转换/L1缓存)并行访问可以完全流水线化,这样每个时钟都可以完成一个加载/存储。

4. 执行L1 TLB查找的指令访问与数据访问是并行的。

5. 所有L1 TLB条目都是驻留在L2 MMU中的TLB条目的一个适当子集。

6. 自动执行失效操作,以保持L2 TLB的一致性。

L2-MMU特性:

1. 16个条目,完全关联的统一的L2 TLB数组(用于指令和数据访问)TLB1支持9种(E500v1)或11种(E500v2)页面大小,即TLB1,用于段式映射。

2. 256表项2-way (E500v1)或512-entry 4-way (E500v2)集关联统一L2 TLB array (TLB0)仅支持4kbyte的页面,即TLB0,用于进行页式映射。

3.对 TLB miss异常的支持。

4. TLB1和TLB0由tlbre, tlbwe, tlbsx, tlbsync, tlbivax和mtspr指令进行管理。

5. 执行由当前核心tlbivax指令产生的TLB1和TLB0失效。支持TLB1和TLB0由其他核心执行的tlbivax指令导致的失效操作。

6. TLB1中实现的IPROT位防止了无效,从而保护关键表项(通过设置IPROT位来指定)不会失效。

2.1 Effective-to-Real Address Translation流程

Effective-to-Real Address Translation(虚拟地址到物理地址的翻译)流程如下所示:

因为E500最小页的大小是4 Kbytes,所以低12位通常被用做4K页内的索引并且不需要进行翻译。首先检查L1 MMU(指令或数据)是否命中地址翻译。如果没有,翻译请求将被转发到(指令和数据)L2 MMU中进行处理。

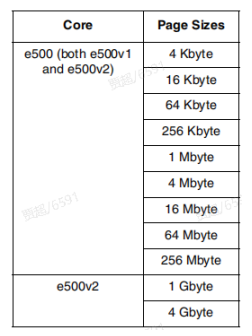

E500v1核心和E500v2核心支持的页大小可见下表,E500v2核心比E500v1核心多支持了1Gbyte和4Gbyte页的大小。

2.2 MMU entry字段

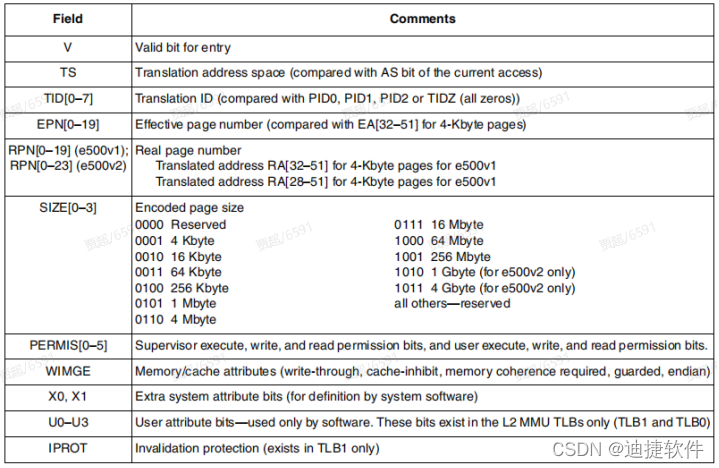

在TLB中,数据都是按行存放的,一行称之为一个entry。一个entry包含了若干bit位下面是MMU entry的bit位含义描述:

V:用来表示当前entry是否有效。为0时表示无效,为1时表示有效。在系统reset之后,所有entry的V位都设为0。

TS:上面地址空间中的AS。为0表示地址空间0,为1表示地址空间1。

TID[0:7]:上面地址空间中的PID。TID为0时,忽略PID的比较。在Linux中,全为0。

EPN[0:19]:虚拟页桢号。根据页大小不同,有效的位数页不同。

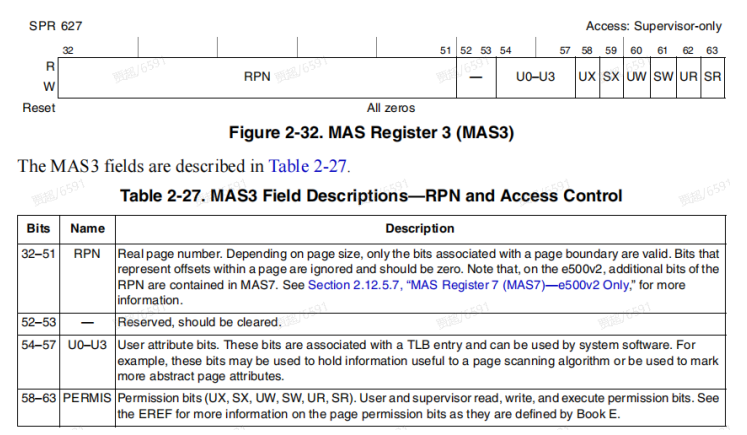

RPN[0:19]:物理页桢号。

SIZE[0:3]:表示当前entry的页大小。

PERMIS[0:5]:用于描述当前entry的访问控制位。分别是UR,SR,UW,SW,UX,SX。分别表示用户态和内核态的读/写/执行权限。

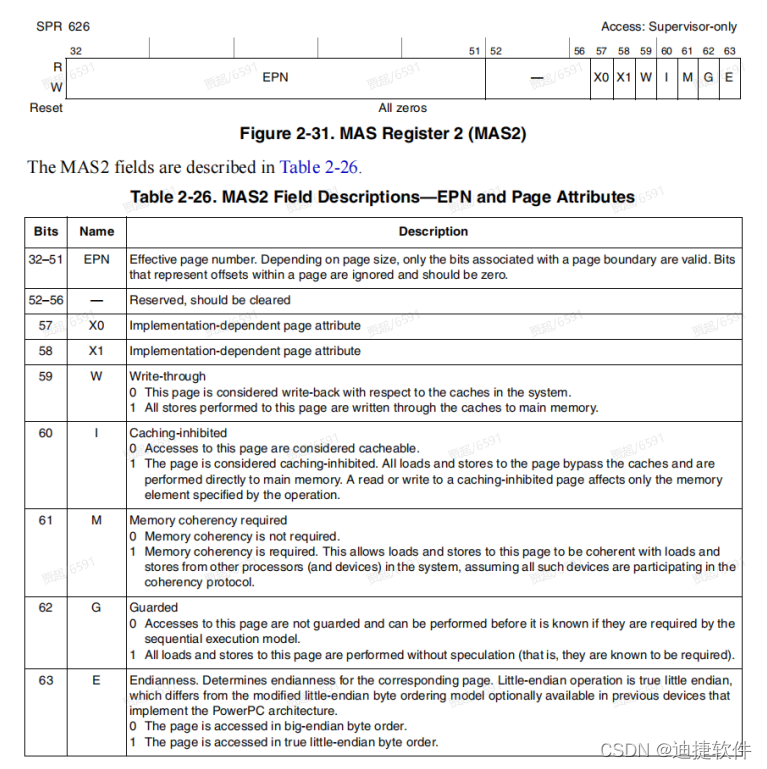

WIMGE[0:4]:W表示当前entry是write through还是write back。I表示当前entry是否忽略Cache。M表示对此数据区的访问需要进行存储一致性处理。G表示对相应存储区域进运行保护。E表示当前entry是小端还是大端。

X0,X1:描述一些额外属性。

U[0:3]:自定义用途。

IPROT:当IPROT为1时,表示当前entry被保护。不能使用tlbivax指令无效该entry。只能用tlbwe指令清除。在E500中只有TLB1支持该位,在TLB0中,该位一直为0。

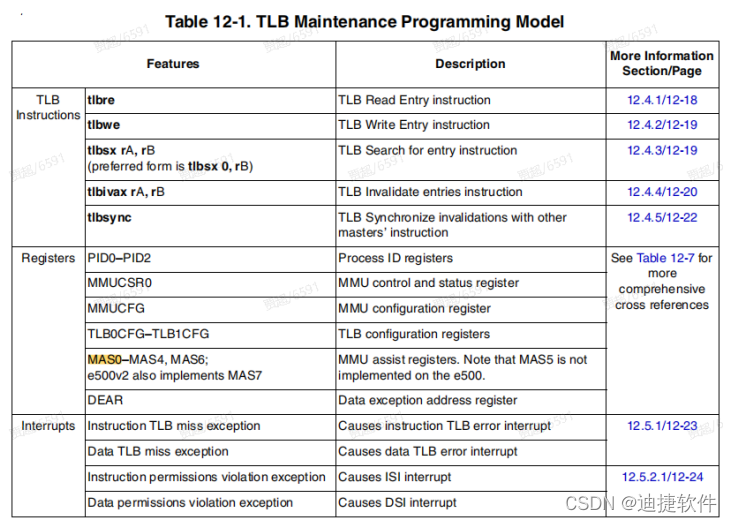

TLB相关指令、寄存器和异常如下表所示:

2.3 MMU相关寄存器

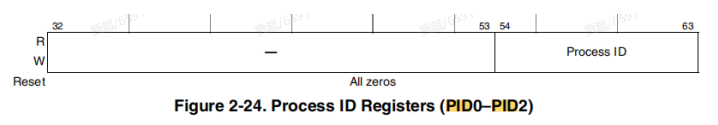

PID0-2寄存器:用于保存当前进程的PID,该寄存器只有54-63位有效。

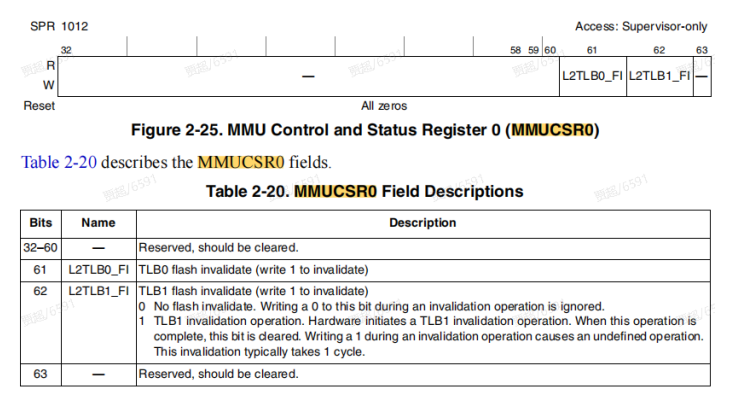

MMUCSR0寄存器:用于使TLB0和TLB1的所有entry无效。该寄存器L2TLB0_FI位使无效TLB0的所有entry;L2TLB1_FI位使无效TLB1的所有entry。

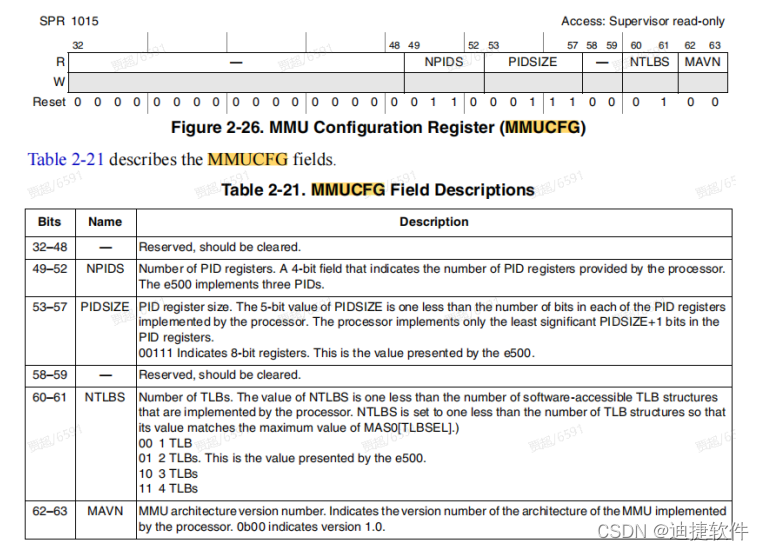

MMUCFG寄存器:用来保存当前MMU的配置信息,包括PID寄存器数量,大小,TLB的数量等。

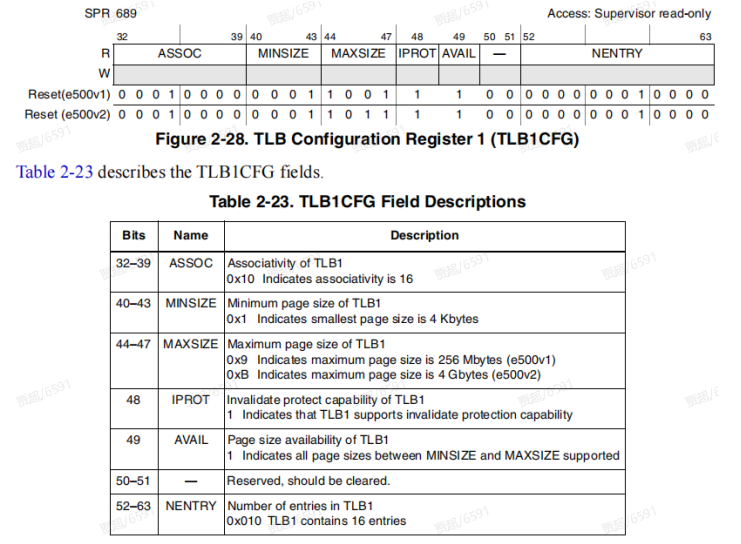

TLB0CFG和TLB1CFG寄存器:用于描述TLB0和TLB1的配置信息,包括entry数量,页表大小等信息。

MAS辅助寄存器(MAS0–MAS4, MAS6–MAS7,没有实现MAS5),主要作用就是维护MMU中TLB的entry。

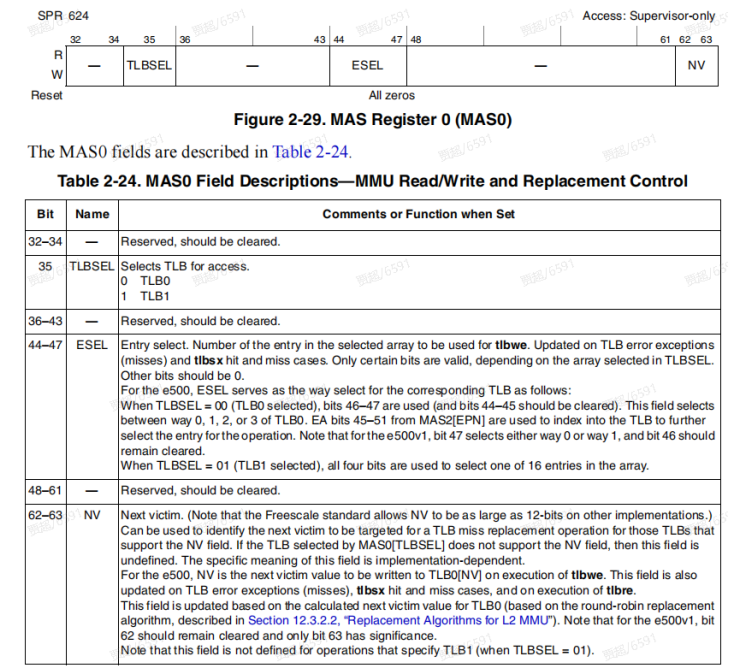

MAS0寄存器:决定写哪个TLB的哪个entry。TLBSEL字段用于选择要操作的TLB,0表示TLB0,1表示TLB1。ESEL字段用于选择TLB的entry。当使用TLB1 时,ESEL字段中低4位有效,用于选择TLB1中的entry。当使用TLB0时,ESEL中只有最低位有效,因为TLB0是两路组相连。NV位用于确定如何替换TLB0中的entry。

MAS1-3中存放的各个字段与TLB entry中的各个字段一一对应。

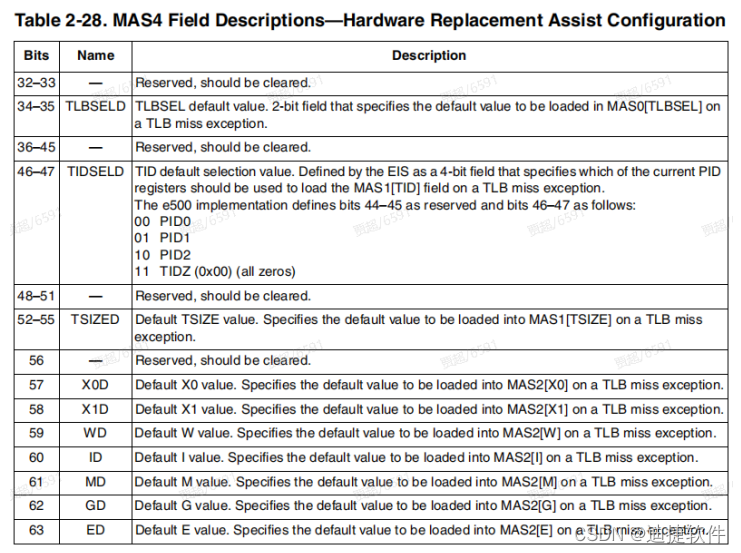

MAS4寄存器

该寄存器主要用于存放当TLB miss异常发生时,对MAS0-3寄存器自动加载而使用的默认值,也就是说MAS4寄存器的内容是硬件写入的。为了提高TLB miss异常的效率,在异常出现时,E500会用MAS4寄存器中的值,自动填写MAS0-2寄存器中的一部分内容:

MAS0[TLBSEL] <- MAS4[TLBSELD]

MAS1[TID] <- MAS4[TIDSELD]

MAS1[TSIZE] <- MAS4[TSIZED]

MAS2[X0,X1] <- MAS4[X0D,X1D]

MAS2[WIMGE] <- MAS4[WD,ID,MD,GD,ED]

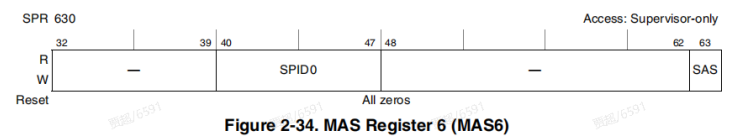

MAS6寄存器:用于对TLB进行检索,MAS6寄存器提供SPID0和SAS,也就是PID和AS字段。

MAS7寄存器(只E500v2支持):包含实现的RPN的高阶地址位支持超过32位的物理地址。

2.4 TLB相关指令和实现

SkyEye,中文全称天目全数字实时仿真软件,是基于可视化建模的硬件行为级仿真平台,支持用户通过拖拽的方式对硬件进行行为级别的仿真和建模。SkyEye支持PowerPC架构E500处理器的指令集仿真,为了支持运行包含MMU单元的操作系统(例如VxWorks、Linux等),需要实现对MMU的仿真功能,其中包含TLB(Translation Lookaside Buffer,转换检测缓冲区)相关的指令实现和MMU虚实翻译过程。

与TLB相关的指令如下:

tlbre指令:tlbre指令是从L2 MMU中读取单个TLB条目的各字段内容,并写入到MMU辅助(MAS)寄存器的相应字段中。读取的entry条目是由MAS0的TLBSEL、ESEL和MAS2寄存器的EPN字段指定,在读TLB1时,ESEL有效,EPN无效;在读TLB0时,ESEL高2位有效,EPN有效。注意,对于E500v2,如果HID0[EN_MAS7_UPDATE] = 1, MAS7也被更新为TLB表项的物理地址。

tlbwe指令:该指令是从MMU辅助寄存器(MAS)中提取各字段内容并写入到L2 MMU中的单个TLB条目中。写入的entry条目是由MAS0的TLBSEL、ESEL和MAS2寄存器的EPN字段指定,在写TLB1时,ESEL有效,EPN无效;在写TLB0时,ESEL高2位有效,EPN有效。注意,对于E500v2,MAS7中的RPN字段也写入到选定的TLB条目中 。

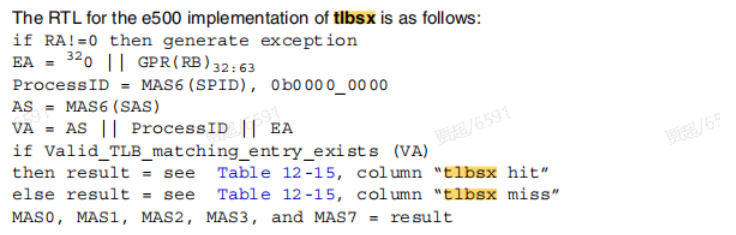

tlbsx指令:指令格式为tlbsx RA,RB。指令作用是使用RA+RB的地址,配合MAS6寄存器对TLB进行查找,如果命中,则将结果放入MAS0-3寄存器。

指令实现:

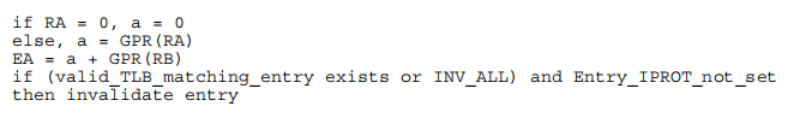

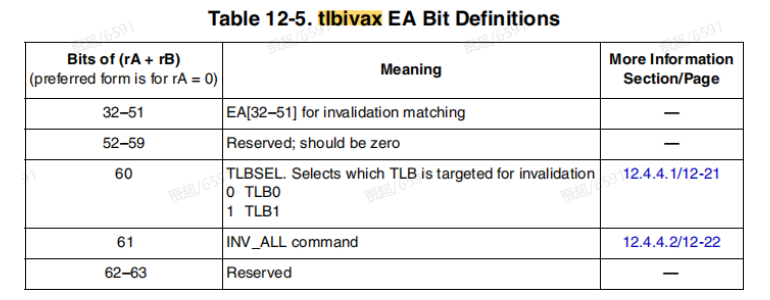

tlbivax指令:TLB无效操作,这条指令将使所有与此计算出的虚拟地址相对应的TLB表项失效,同样也会使其他处理器上TLB中包含的TBL表项失效。

根据有效地址EA的Bit61位决定是否是无效全部的entry,如果不是,计算出相对应的entry,然后设置entry->v = 0用于使表项失效。

tlbsync指令:该指令用于同步对TLB entry的读写。主要用途是将tlbivax指令的更新entry广播到系统总线上,用来同步其他处理器,该指令只在SMP系统中有效。

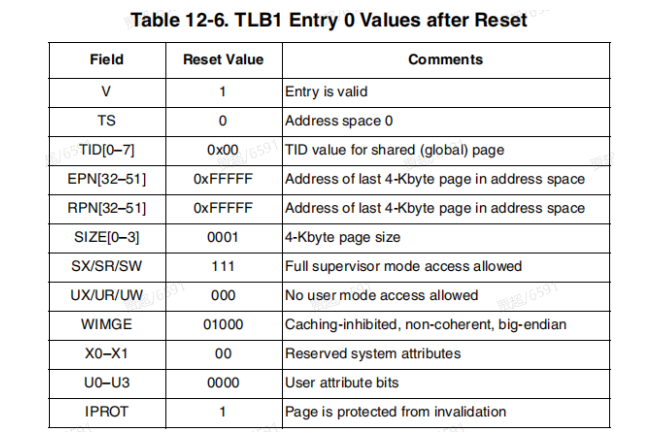

2.5 系统复位后的TLB初始状态

复位后,L1和L2 MMU中的TLB表项全部失效,TLB1的第一个entry需要初始化赋值,如下所示:

参考文献:

[1] PowerPC™ e500 Core Family Reference Manual.pdf